# CZECH TECHNICAL UNIVERSITY IN PRAGUE

Faculty of Electrical Engineering Department of Circuit Theory

# **DOCTORAL** THESIS **Analog Circuits for DC-DC Converters**

February 2018

Author: Supervisor: Ing. Martin Dřínovský doc. Dr. Ing. Jiří Hospodka

Study program:

Electrical Engineering and Information Technology Branch of study: Electrical Engineering Theory

## **Analog Circuits for DC-DC converters**

by

## Martin Dřínovský

Submitted to the Department of Circuit Theory in partial fulfillment of the requirements for the degree Doctor of Philosophy.

#### Abstract

DC-DC converter are essential part in a whole range of applications. With the continuous integration and demand for higher efficiency more strict requirements are put on various circuits that make up the converter. The thesis pursues three circuit areas, current sensors, oscillators, zero crossing and overcurrent detectors.

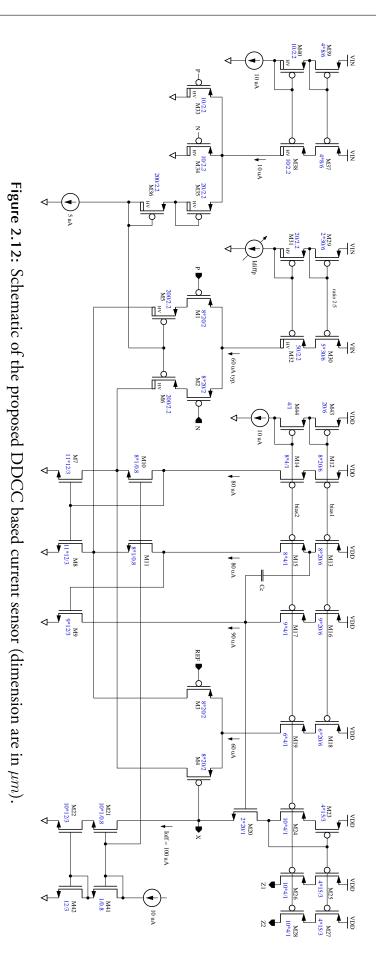

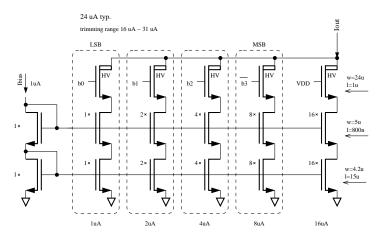

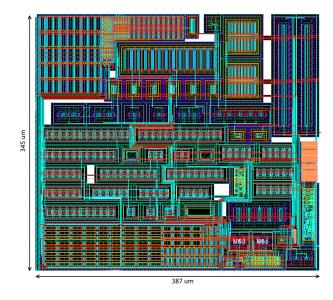

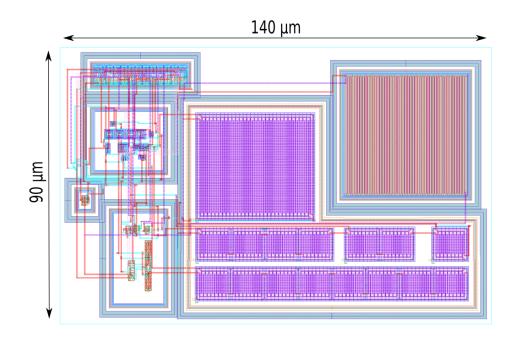

Current sensors are used for overcurrent protection, regulation and in case of multiphase converters for balancing. A new high voltage current sensor for coil-based current sensing in DC-DC converters is presented. The sensor employs DDCC with high voltage input stage and gain trimming. The circuit has been simulated and implemented in 0.35  $\mu$ m BCD technology as part of a multiphase DC-DC converter where its function has been verified. The circuit is able to sustain common mode voltage on the input up to 40 V while it occupies  $0.387 \times 0.345$  mm<sup>2</sup>.

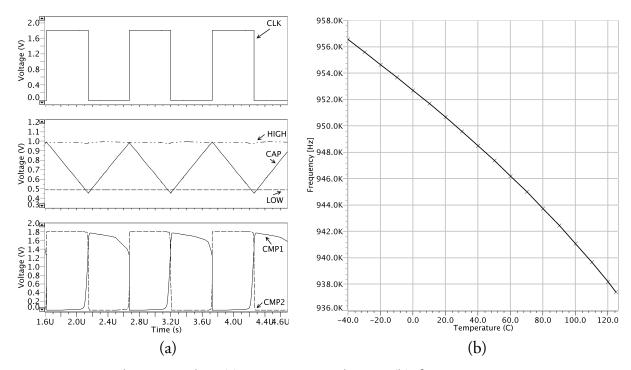

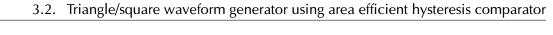

In the second part, a function generator generating both square and triangle waveforms suitable for DC-DC converters is proposed. The generator employs only one low area comparator with accurate hysteresis set by a bias current and a resistor. Oscillation frequency and its non-idealities are analyzed. The function of the proposed circuit is demonstrated on a design of 1 MHz oscillator in STMicroelectronics 180 nm BCD technology. The designed circuit is thoroughly simulated including trimming evaluation. It consumes 4.1  $\mu$ A at 1.8 V and takes 0.0126  $mm^2$  of silicon area. The temperature variation from  $-40 \,^{\circ}$ C to  $125 \,^{\circ}$ C is  $\pm 1.5 \,^{\circ}$  and the temperature coefficient is 127 ppm/ $^{\circ}$ C.

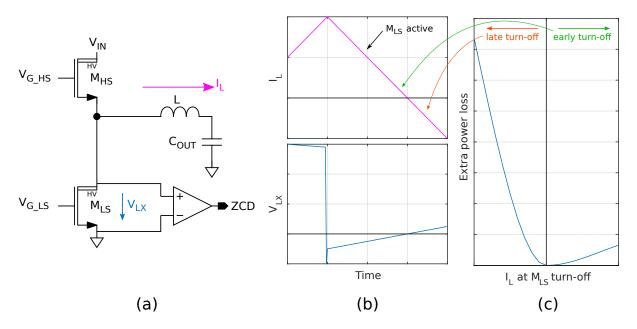

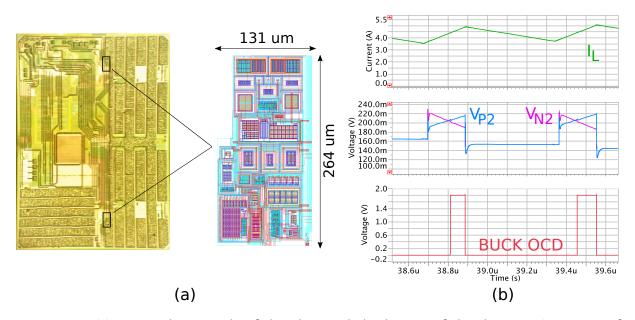

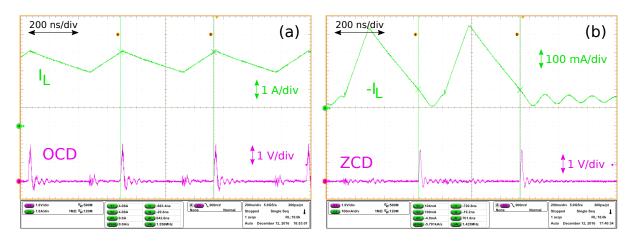

In the third part, a dual purpose over-current (OCD) and zero crossing detector (ZCD) for high voltage switching DC-DC battery chargers is presented. As in both buck and boost operation modes the current is sensed on high side power transistor it is possible to reuse the detection circuit which inherently saves silicon area. The circuit was designed in STMicroelectronics 0.18  $\mu$ m BCD technology and occupies only 0.035 mm<sup>2</sup> while consuming 1.2 mW operating from 12 V power supply. The correct operation of the circuit was verified on silicon as part of a dual-phase battery charger.

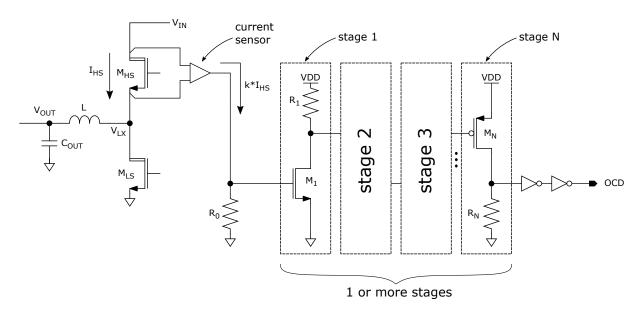

The last presented circuit is an overcurrent detector with built-in reference and programmable threshold. It features a built-in detection threshold set by a  $V_{GS}$  of a MOS transistor and a resistor value R. The main benefits of this solution are lack of kickback noise on reference bias line, low power operation – consumes only when sensing current, high speed, and small area. All these properties are essential for ultra-low power converters. The circuit was designed in the same 0.18  $\mu$ m BCD technology and its operation was verified on silicon. It occupies 0.011 mm<sup>2</sup> and consumes 16  $\mu$ A static current (at zero inductor current).

Keywords: DC-DC converter, current sensor, oscillator, comparator

#### Abstrakt

DC-DC měniče jsou nepostradatelnou součástí řady aplikací. Vzhledem k neustálé integraci a požadavkům na vyšší účinnost jsou kladeny stále vyšší nároky na vnitřní obvody těchto měničů. Tato dizertační práce se zabývá třemi oblastmi: proudovými senzory, oscilátory, komparátory průchodu nulou a nadproudovými komparátory.

Proudové senzory se využívají pro nadproudovou ochranu, regulaci a v případě vícefázových měničů pro balancování fází. Nový vysokonapěťový proudový senzor pro měření proudu cívkou v DC-DC měničích je představen. Senzor využívá DDCC proudový konvejor s vysokonapěťovými vstupy a kalibrovatelným ziskem. Obvod byl simulován a implementován v  $0.35 \ \mu m$  BCD technologii jako součást vícefázového DC-DC měniče, v rámci něhož byla jeho funkce ověřena. Obvod vydrží na vstupu souhlasné napětí až 40 V a zabírá na chipu  $0.387 \times 0.345 \ mm^2$ .

Ve druhé části je představen funkční generátor generující trojúhelníkový i obdélníkový signál vhodný pro DC-DC měniče. Generátor využívá jeden komparátor optimalizovaný na plochu s hysterezí nastavitelnou proudem a odporem. Výstupní frekvence a její závislosti jsou zanalyzovány. Funkční generátor s frekvencí 1 MHz je navržen v 180 nm BCD technologii společnosti STMicroelectronics. Funkce obvodu je doložena simulacemi včetně kalibrace. Teplotní variace frekvence od -40 °C do 125 °C je  $\pm 1.5$  % a teplotní koeficient je 127 ppm/°C.

Ve třetí části je prezentován kombinovaný nadproudový detektor (OCD) a detektor průchodu nulou (ZCD) pro vysokonapěťové spínané měniče pro nabíjení baterií. Jelikož oba detektory v buck i boost módu snímají proud na výkonovém tranzistoru připojeném ke stejnému vstupnímu, resp. výstupnímu uzlu, je možné oba dva detektory sloučit do jednoho pro ušetření plochy na chipu. Obvod byl navržen rovněž v 180 nm BCD technologii, zabírá plochu 0.035 mm<sup>2</sup> a spotřebuje 1.2 mW při 12 V napájecím napětí. Obvod byl vyroben jako součást dvoufázového obvodu pro nabíjení baterií a jeho funkce byla ověřena měřením.

Posledním prezentovaným obvoden je nadproudový detektor s vestavěnou referencí a programovatelným detekčním limitem nastaveným pomocí  $V_{\rm GS}$  napětí MOS tranzistoru a rezistoru R. Hlavními výhodami tohoto řešení je absence rušení do reference, nízký odběr, vysoká rychlost a malá plocha. Všechny tyto vlastnosti jsou nutné v měničích s velice nízkou spotřebou. Obvod byl navržen ve stejné 180 nm BCD technologii a jeho funkce byla ověřena měřením. Obvod zabírá 0.011 mm<sup>2</sup> na chipu a má statickou spotřebu 16 µA (při nulovém proudu cívkou).

Klíčová slova: DC-DC měnič, proudový senzor, oscilátor, komparátor

## Acknowledgements

This thesis was created while I was working for STMicroelectronics. I would like to thank all the staff and people who supported me and foremost my colleagues I had the pleasure to work with on the projects that carry some of the solution presented in this thesis. Namely, these are Jindřich Duda, Michal Paulen, Jan Kudrnka and René Grossmann. Equally I would like to thank layouters that took good care of the layout work for the presented circuits, application engineers that allowed me to to take measurements and other people who gave me support.

My greatest thank belongs to Jiří Hospodka who supervised the thesis, gave me advice and always encouraged me to continue and pursue the studies.

Most importantly, I would like to thank my family for support they are giving me for all my life.

I hereby declare that I have created this thesis on my own and exclusively using literature presented in the references. I agree with lending and publishing this work or its parts.

## Contents

| Co | ntents                                                                                                                                                                                             | i                          |  |  |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|

| Li | t of Figures                                                                                                                                                                                       | ii                         |  |  |  |

| Li | t of Tables                                                                                                                                                                                        | iv                         |  |  |  |

| Sy | nbols and Abbreviations                                                                                                                                                                            | vi                         |  |  |  |

| 1  | Introduction1.1Linear voltage regulators1.2Switching converters1.3Anatomy of switching converters1.4Thesis motivation1.5Goals of the thesis1.6Organization                                         | . 3<br>. 5<br>. 11<br>. 12 |  |  |  |

| 2  | Current Sensors2.1 On-chip inductor current sensing2.2 Off-chip inductor current sensing2.3 Analysis of a DDA2.4 High voltage coil current sensor employing DDCC2.5 Summary                        | . 18<br>. 20<br>. 27       |  |  |  |

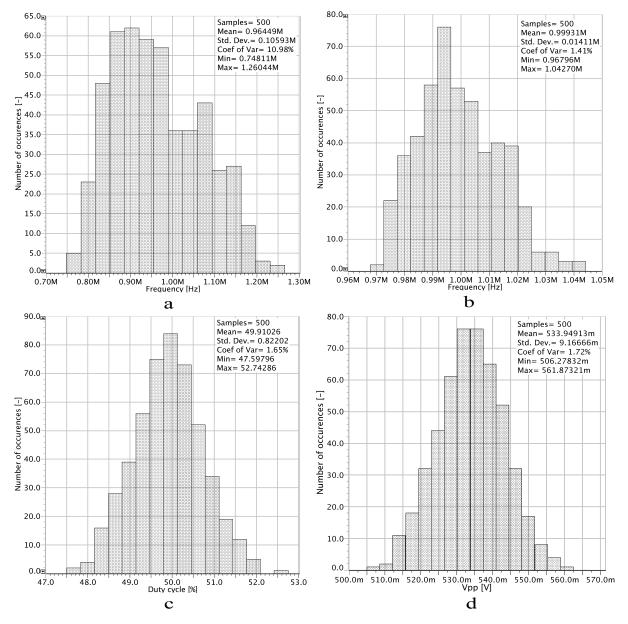

| 3  | Oscillators3.1Triangular relaxation oscillators3.2Triangle/square waveform generator using area efficient hysteresis compara3.3Summary                                                             | tor 34                     |  |  |  |

| 4  | Current Comparators4.1Zero crossing detectors4.2Over current detectors4.3Dual purpose HV buck OCD/boost ZCD for portable battery chargers4.4Overcurrent detector with built-in reference4.5Summary | . 45<br>. 47<br>. 52       |  |  |  |

| 5  | Conclusion                                                                                                                                                                                         |                            |  |  |  |

| Au | Author's Publications                                                                                                                                                                              |                            |  |  |  |

| Bi | Bibliography                                                                                                                                                                                       |                            |  |  |  |

# List of Figures

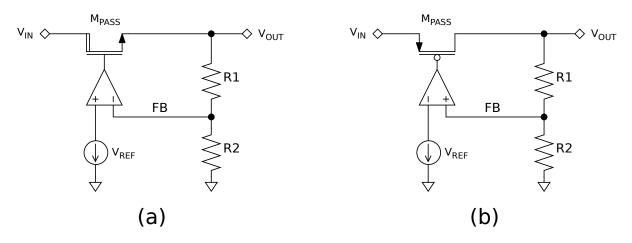

| 1.1        | Block diagram of linear voltage regulators: (a) conventional, (b) low drop-out.                                                                               | 3          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.2        | Topologies of SMPS converters: (a) buck , (b) boost                                                                                                           | 4          |

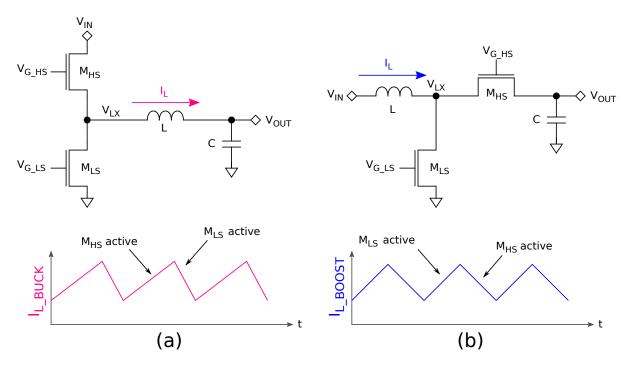

| 1.3        | Block diagram of buck converter.                                                                                                                              | 6          |

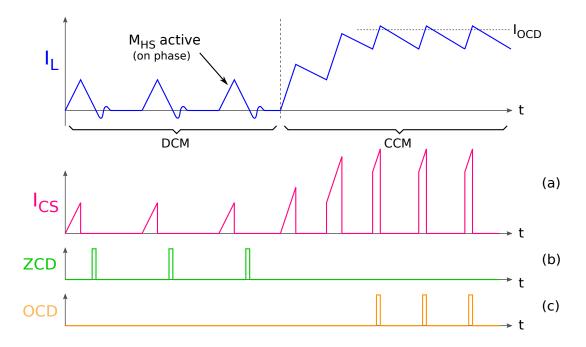

| 1.4        | Inductor current waveform along with (a) current sensor (on phase sensing),<br>(b) ZCD and (c) OCD outputs (not to scale).                                    | 7          |

| 1.5        | Control types: (a) Voltage mode control (VMC), (b) current mode control (CMC).                                                                                | 9          |

| 2.1        | Sense/copy MOS current sensing technique.                                                                                                                     | 15         |

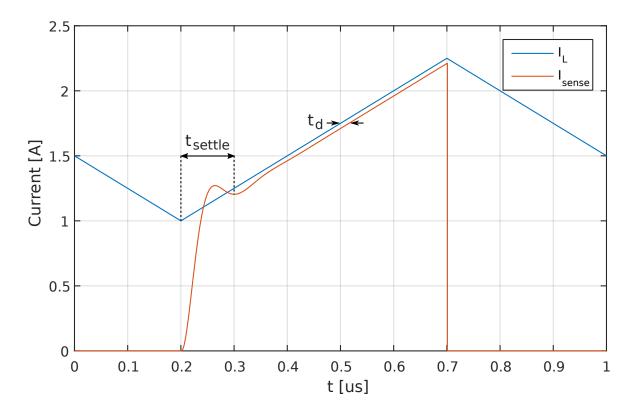

| 2.2        | High-side current sensor transient response example                                                                                                           | 16         |

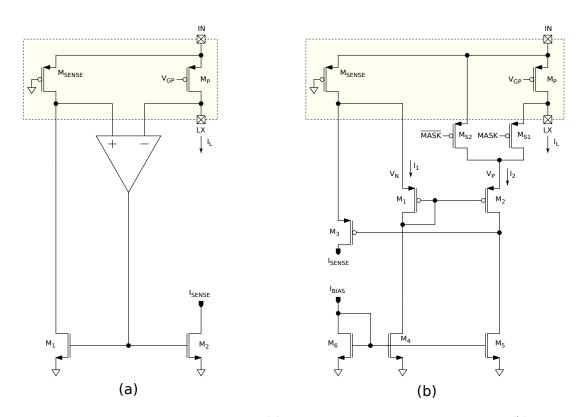

| 2.3        | Sense MOS current sensor topologies                                                                                                                           | 17         |

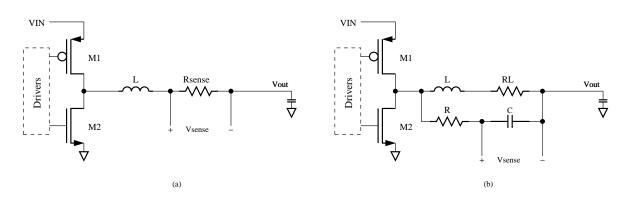

| 2.4        | Off-chip inductor current sensing                                                                                                                             | 18         |

| 2.5        | Off-chip sensing architectures                                                                                                                                | 19         |

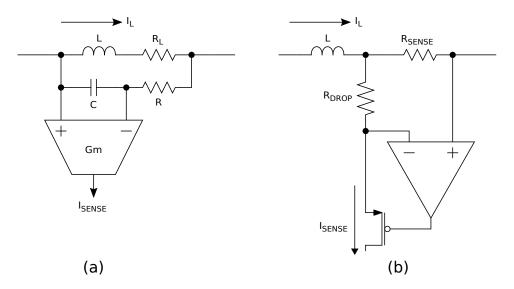

| 2.6        | Block diagram of a DDCC based current sensor.                                                                                                                 | 20         |

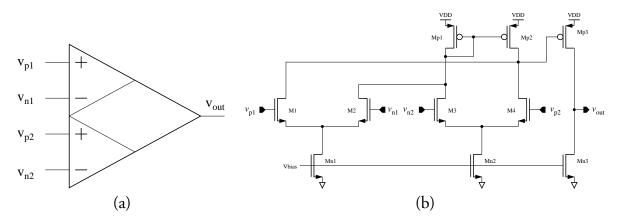

| 2.7        | Differential difference amplifier: (a) symbol, (b) example of CMOS implemen-<br>tation.                                                                       | 21         |

| 2.8        | Dependence of the transconductance of a differential pair on input voltage                                                                                    | <i>L</i> 1 |

| 2.0        | difference for various bias conditions.                                                                                                                       | 22         |

| 2.9        | Simplified block diagram of DDA in unity gain configuration with major non-                                                                                   |            |

| 2.)        | idealities.                                                                                                                                                   | 23         |

| 2.10       | Nonlinearity with gain mismatch.                                                                                                                              | 26         |

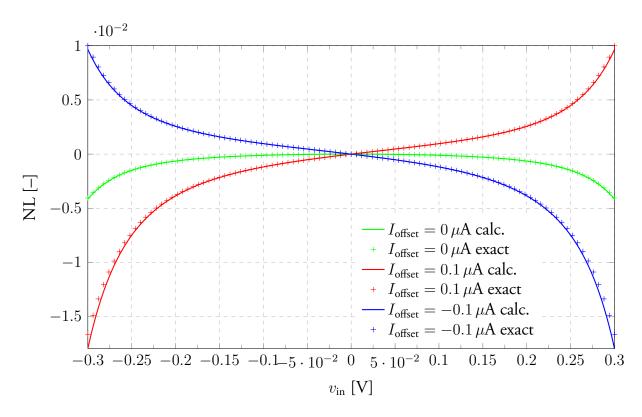

| 2.11       | Nonlinearity with offset                                                                                                                                      | 26         |

| 2.12       | Schematic of the proposed DDCC based current sensor (dimension are in $\mu m$ ).                                                                              | 28         |

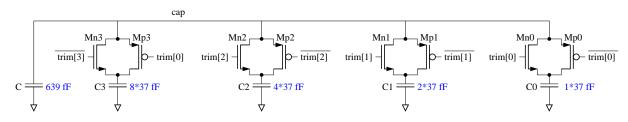

| 2.13       | Gain trimming DAC (dimensions apply for entire rows)                                                                                                          | 29         |

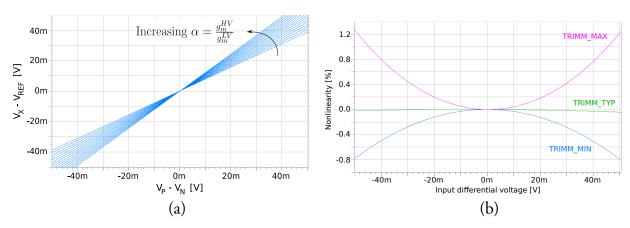

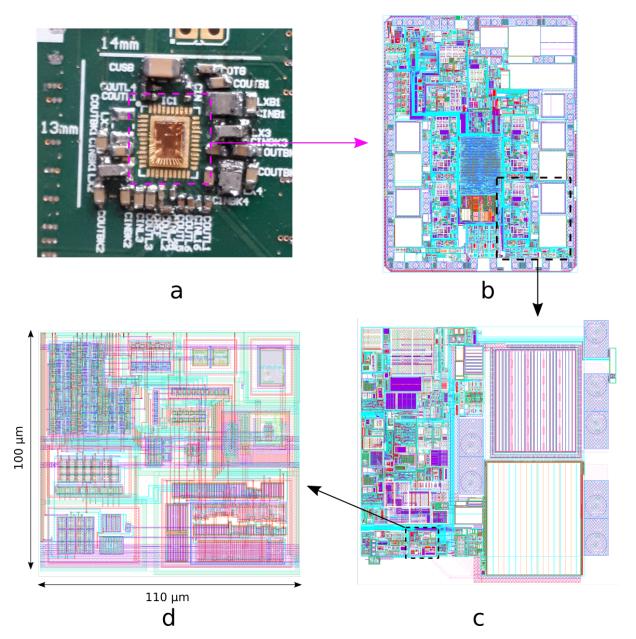

|            | Layout of the proposed circuit (courtesy of STMicroelectronics) (a) Transfer characteristics, (b) achieved nonlinearity $(I_{sim}/I_{ideal}-1)$ for different | 29         |

| 2.1)       | trimming steps                                                                                                                                                | 30         |

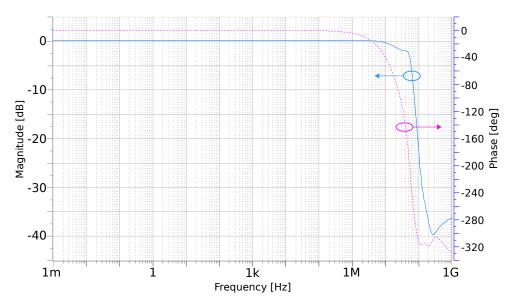

| 2 16       | Gain and phase characteristics of $V_X/V_{sense}$ .                                                                                                           | 30         |

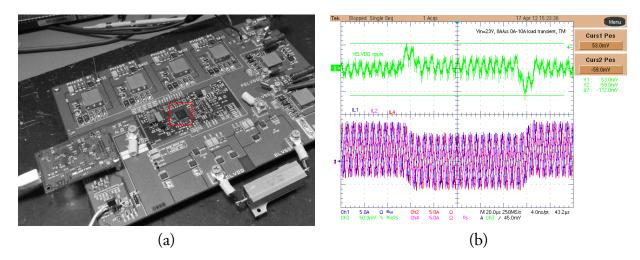

|            | (a) Application board with the device (mark in square) featuring the proposed                                                                                 | 50         |

|            | current sensor, (b) output voltage and current of three phases balanced with the                                                                              | 21         |

|            | help of the proposed sensor (images courtesy of STMicroelectronics)                                                                                           | 31         |

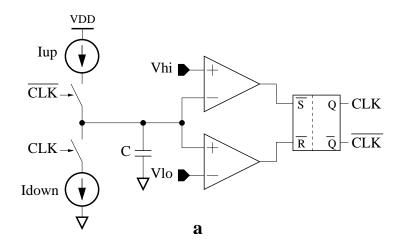

| 3.1        | Conventional triangle generating oscillator                                                                                                                   | 32         |

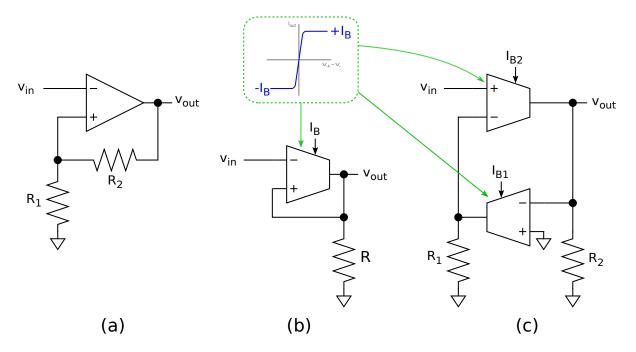

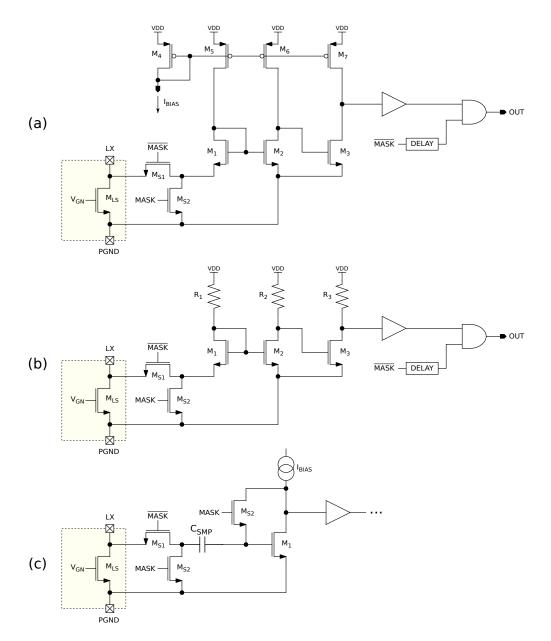

| 3.2        | Hysteresis comparators: (a) [32], (b) [33], (c) [34]                                                                                                          | 33         |

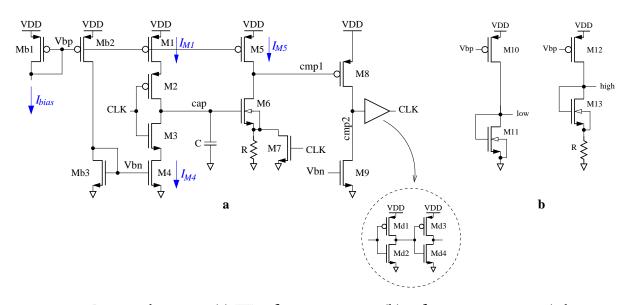

| 3.3        | Proposed circuit: (a) Waveform generator, (b) reference generators (when not explicitly shown the bulks are tied to $V_{DD}$ or ground for PMOS and NMOS,     |            |

|            |                                                                                                                                                               | 35         |

| 3.4        | respectively)                                                                                                                                                 | 36         |

| 3.5        | Trimming circuit.                                                                                                                                             | 38         |

| 5.5<br>3.6 | Simulation results: (a) transient simulation, (b) frequency temperature variation.                                                                            | 50<br>38   |

| 3.7        | Monte Carlo analysis histograms: (a) Frequency before trimming, (b) frequency                                                                                 | 90         |

| J./        | after trimming, (c) duty cycle, (d) peak-to-peak output voltage                                                                                               | 39         |

|            | arei immining, (c) uuty cycle, (u) peak-to-peak output voltage.                                                                                               | 5)         |

| 4.1                                                                                | ZCD sensing                                                                 |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 4.2                                                                                | ZCD circuits                                                                |

| 4.3                                                                                | OCD architectures                                                           |

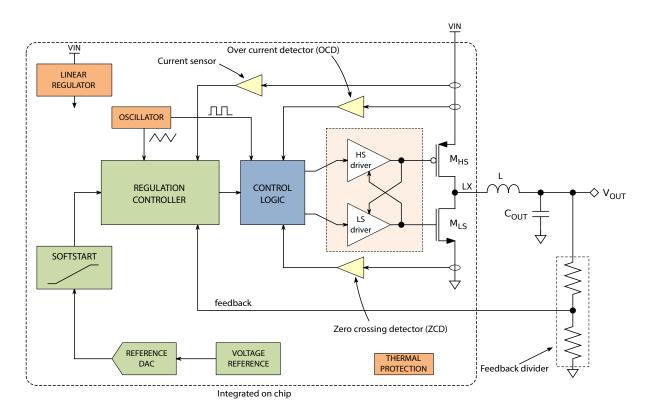

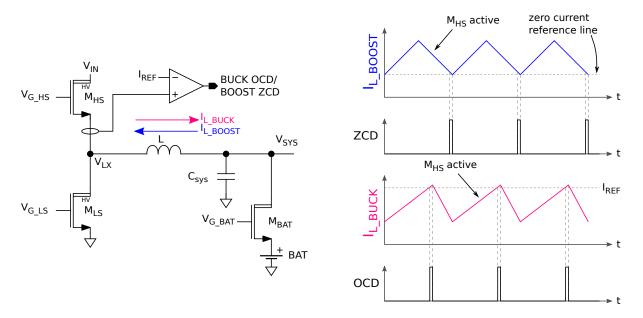

| 4.4                                                                                | Battery charger system block diagram 47                                     |

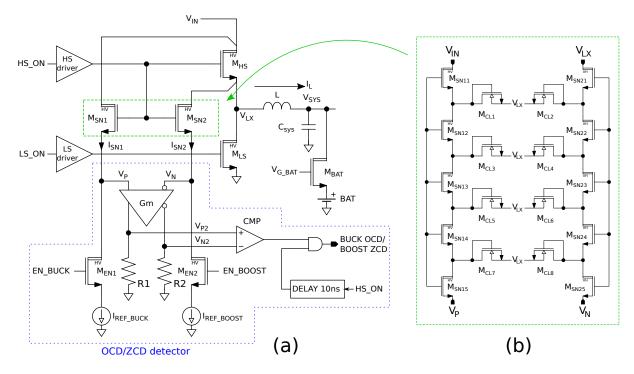

| 4.5                                                                                | Combined OCD/ZCD detector                                                   |

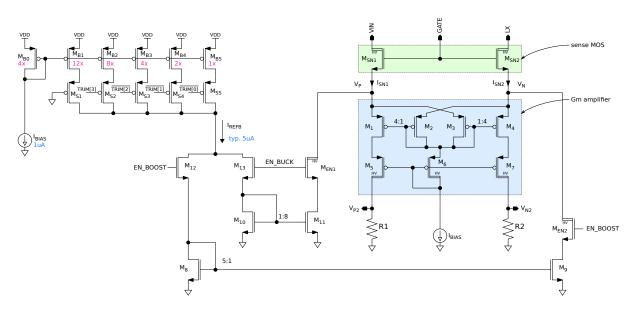

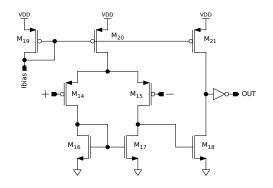

| 4.6                                                                                | Schematic of the Gm amplifier and reference current sources                 |

| 4.7                                                                                | Schematic of the comparator CMP                                             |

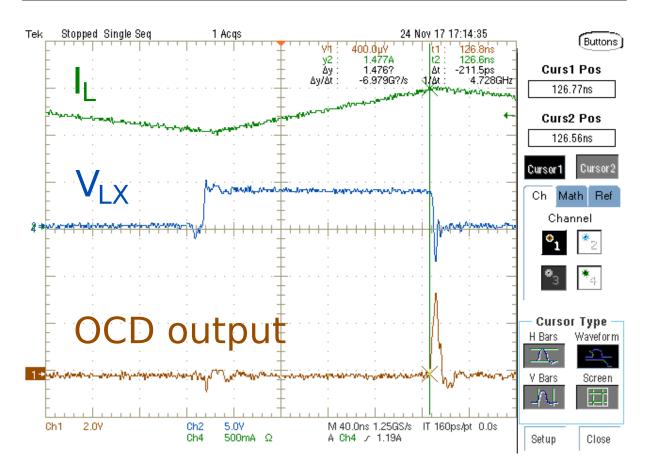

| 4.8                                                                                | Microphotograph of the chip and simulation results                          |

| 4.9 Oscilloscope screenshot of the detector operation in: (a) buck mode, (b) boost |                                                                             |

|                                                                                    | mode                                                                        |

| 4.10                                                                               | Block diagram of the circuit                                                |

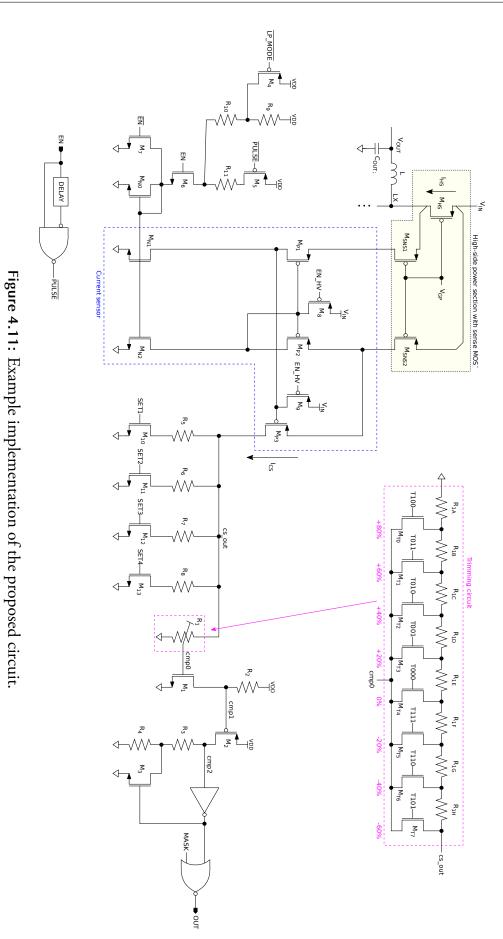

| 4.11                                                                               | Example implementation of the proposed circuit                              |

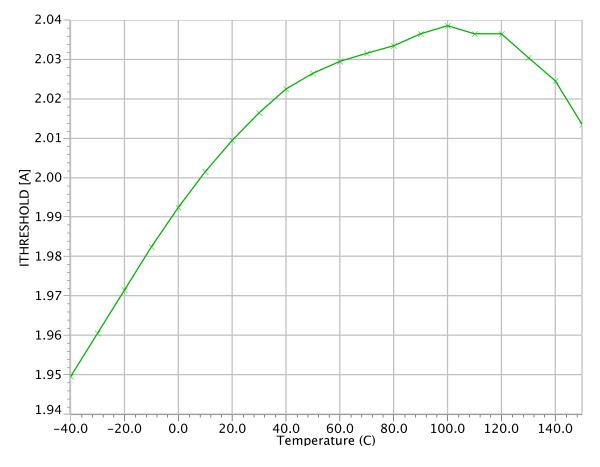

| 4.12                                                                               | Temperature sweep simulation result                                         |

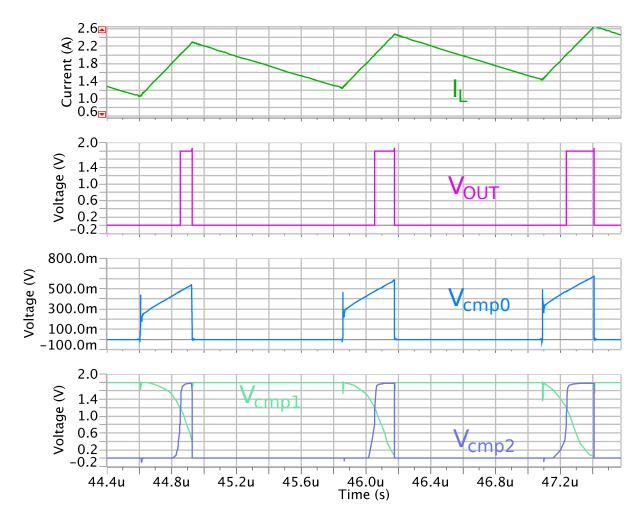

|                                                                                    | Transient simulation result                                                 |

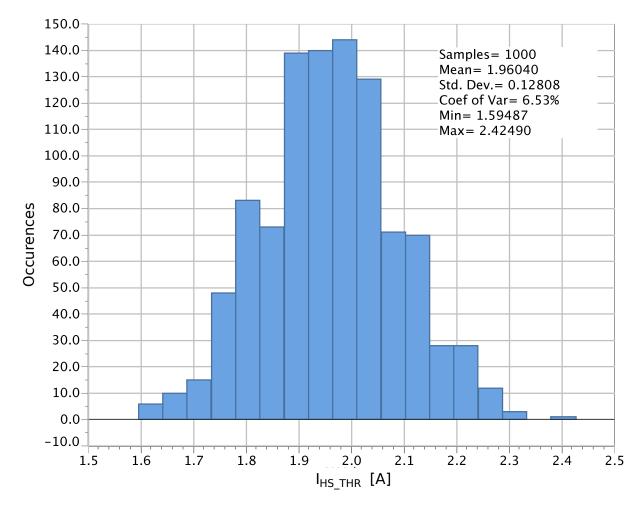

|                                                                                    | Monte Carlo simulation of current threshold spread (statistical corners) 58 |

|                                                                                    | Photo and layout of the designed OCD                                        |

| 4.16                                                                               | Oscilloscope screenshot showing the OCD operation for 1.5 A setting 60      |

|                                                                                    |                                                                             |

## List of Tables

| Comparison of selected architectures                    |  |

|---------------------------------------------------------|--|

| Contribution of different branches on current threshold |  |

# Symbols and Abbreviations

| ASIC              | Application specific integrated circuits.                                |

|-------------------|--------------------------------------------------------------------------|

| BCD               | Bipolar, CMOS, DMOS (technology).                                        |

| BJT               | Bipolar junction transistor.                                             |

| ČСМ               | Continuous conduction mode.                                              |

| CCII              | Current conveyor, second generation.                                     |

| C <sub>gd</sub>   | MOS gate-drain capacitance.                                              |

| $C_{gs}$          | MOS gate-source capacitance.                                             |

| COB               | Chip on board.                                                           |

| C <sub>ox</sub>   | MOS gate oxide capacitance per unit area.                                |

| CMC               | Current mode control.                                                    |

| D                 | Duty cycle.                                                              |

| DAC               | Digital to analog converter.                                             |

| DCR               | DC resistance (of inductor).                                             |

| DCM               | Discontinuous conduction mode.                                           |

| DDCC              |                                                                          |

| DDCC              | Differential difference current conveyor.                                |

|                   | Discontinuous mode detector (synonym to ZCD).                            |

| DMOS              | Double diffused MOS (MOS transistor structure to support high voltages). |

| EMI               | Electromagnetic interference.                                            |

| HS                | (Referred to) low-side (switching inductor to input of output).          |

| HV                | High voltage.                                                            |

| LDO               | Low drop-out regulator.                                                  |

| LS                | (Referred to) low-side (switching inductor to ground).                   |

| LX                | Inductor switched node.                                                  |

| MC                | Monte Carlo (analysis).                                                  |

| MOS               | Metal-oxide-semiconductor transistor.                                    |

| OCD               | Overcurrent detector.                                                    |

| OCP               | Overcurrent protection (same as OCD).                                    |

| OTA               | Operational transconductance amplifier.                                  |

| PCB               | Printed circuit board.                                                   |

| PFM               | Pulse frequency modulation.                                              |

| PMIC              | Power management integrated circuits.                                    |

| PSR(R)            | Power supply rejection (ratio).                                          |

| PVT               | Process, voltage, temperature (variations).                              |

| PWM               | Pulse width modulation.                                                  |

| R <sub>dson</sub> | MOS on-state drain-source resistance.                                    |

| SMPS              | Switch mode power supply.                                                |

| t <sub>pd</sub>   | Propagation delay.                                                       |

| ŪSΒ               | Universal serial bus.                                                    |

| U <sub>T</sub>    | Thermal voltage $kT/q$ .                                                 |

| V <sub>GS</sub>   | MOS gate-source voltage.                                                 |

| VT                | MOS threshold voltage.                                                   |

| VMC               | Voltage mode control.                                                    |

| ZCD               | Zero crossing detector.                                                  |

| $\eta$            | Power efficiency.                                                        |

| $\mu$             | MOS carrier mobility.                                                    |

| •                 | ,                                                                        |

## 1 Introduction

Since the advent of electronic circuits, one of the problems was how to supply them with the necessary voltage for their correct operation either from a battery or AC power grid. At the beginning, electromechanical relays and vibrators were used to generate high voltages to supply vacuum tubes. With the invention of transistors circuits capable of generating higher voltages (such as [1]) started to emerge as well as various discrete linear voltage regulators. But it was as late as 1967 when Bob Widlar (Fairchild) designed the first integrated voltage regulator  $\mu$ A723 [2] one of whose applications include a switching regulator. Nowadays voltage regulators, be it linear or switching, are an important class of integrated circuits and are present in portfolios of every major semiconductor manufacturer.

The increasingly complex systems, such as computers, mobile phones or tablets, can utilize tens of switching and linear regulators not only to power different voltage domains but also to isolate different subsystems and guarantee one doesn't influence the other. To save price and area these regulators are usually grouped in complex power management integrated circuits (PMIC) often made as application specific integrated circuits (ASIC) tailored to a specific application for a specific customer.

## 1.1 Linear voltage regulators

Linear voltage regulators convert higher input voltage to a lower output voltage (in absolute values, can be utilized for both positive and negative supply lines). Block diagram can be seen in Fig. 1.1a. The voltage difference (drop-out)  $V_{\rm IN} - V_{\rm OUT}$  is spent on a power transistor  $M_{\rm PASS}$ , which can be either MOS of BJT. The regulating element (operational amplifier) then controls the gate voltage of the power transistor in such a way that the feedback voltage generated by the feedback divider<sup>1</sup> is equal to the reference voltage. Then the output voltage is

$$V_{\rm OUT} = V_{\rm REF} \left( 1 + \frac{R_1}{R_2} \right). \tag{1.1}$$

The feedback resistors can be both external or internal to the chip. The latter case is often used in high volume systems where every external component adds non-negligible cost to the manufacturer. In that case the voltage version is hardwired or preprogrammed in the chip or, as in the case of PMICs, can be programmed directly in application using some configuration protocol.

Although using N channel pass transistor has its benefits (better PSR, wider range of acceptable output capacitors) the drawback is high drop-out (needs at least  $V_{GS}$  higher input supply voltage) around 1 V. To overcome this, the so called low drop-out (LDO) regulators (Fig. 1.1b) use P channel pass transistor which can reach drop-outs below 100 mV.

The advantages of linear regulators include clean, low-noise output, regulation accuracy, good power supply rejection (PSR) or simplicity (low silicon area  $\rightarrow$  cost). However, the major drawback of linear regulators is the power efficiency given as (neglecting quiescent

<sup>&</sup>lt;sup>1</sup> Sometimes the feedback divider is not present and the regulator regulates directly to  $V_{\text{REF}}$ , this configuration is used for example in low-noise regulators.

Figure 1.1: Block diagram of linear voltage regulators: (a) conventional, (b) low drop-out.

current of the regulator)

$$\eta = \frac{P_{\rm OUT}}{P_{\rm IN}} = \frac{V_{\rm OUT}}{V_{\rm IN}}.$$

(1.2)

This is a major drawback for a lot of systems, e.g. battery operated devices, and contributed for the fast development and adoption of switching mode power supplies.

### 1.2 Switching converters

Switching converters, also known as switch mode power supplies (SMPS) or DC-DC converters, use either capacitors<sup>2</sup> or inductors (or transformers) to convey energy between input and output. From an input voltage switching converters can generate lower output voltage and unlike linear regulators some topologies can generate higher output voltage or even negative output voltage. The major advantage of switching converters is their high efficiency (can be higher than 90%) due to which they find place not only in high power applications but also in low power ones, especially battery operated devices, where they complement or even replace previously used linear regulators On the other hand, disadvantages include output ripple, higher noise, lower regulation accuracy and cost (due to the higher complexity of the regulator and the higher component count).

There exist numerous non-isolated (use inductors) and isolated (use transformers) topologies and it is beyond the scope of this thesis to go into detail of all of them. Nevertheless, two of the most important topologies are briefly described next. Curious reader can find detailed analysis of various converters e.g. in [3].

#### **Buck converter**

One of the simplest switching converter topology is the buck converter as depicted in Fig. 1.2a. The energy transfer element is the inductor L whose one pole (the associated node is usually named LX, SW or phase) is switched between input voltage and ground using two switches, here represented by two transistors, high-side  $M_{HS}$  and low-side  $M_{LS}$ .

<sup>&</sup>lt;sup>2</sup>Due to the focus of the thesis capacitor based DC-DC converters are not further described.

Figure 1.2: Topologies of SMPS converters: (a) buck, (b) boost.

The high-side transistor can be both P-channel or N-channel MOS. While NMOS is preferred for its lower on-state resistance ( $R_{dson}$ ) it requires gate voltage higher than  $V_{IN}$  to turn-on. Although there exist methods to overcome this limitation (e.g. using bootstrap capacitor to power the high-side driver) they incur additional area and cost to the system, therefore a PMOS is usually used in place of  $M_{HS}$ . For low-side switch an NMOS is usually used.

To describe the operation of the buck converter let's assume that  $V_{OUT} < V_{IN}$ . When  $M_{HS}$  is active the constant voltage across the inductor (assuming ideal case, i.e. neglecting all switch and coil resistances and ripple on  $V_{OUT}$ ) causes the inductor current to linearly increase with slope  $(V_{IN} - V_{OUT})/L$ . This phase is usually called the active phase or on phase and the duration in one period is denoted  $t_{ON}$ . When  $M_{LS}$  is active the switching node LX is tied to ground and the negative voltage across the inductor causes the current to decrease with slope  $V_{OUT}/L$ . This phase is usually denoted  $t_{OFF}$ .

In both phases the inductor current is flowing to the output and thus the average value of the inductor current is equal to the load current. The value of the output voltage is given by<sup>3</sup>

$$V_{\rm OUT} = D V_{\rm IN},\tag{1.3}$$

where D is the duty cycle, i.e. the ratio of  $t_{ON}$  and the switching period T. The output voltage of the buck converter is therefore always  $V_{OUT} \leq V_{IN}$ . When the input voltage  $V_{IN}$  drops below requested output voltage the high-side switch gets turned-on for the whole period, this mode is usually called bypass mode.

<sup>&</sup>lt;sup>3</sup> Assuming continuous conduction mode (CCM), see next.

#### Boost converter

In contrast to buck converter which generates  $V_{OUT}$  less than  $V_{IN}$ , the boost converter always generates output voltage higher than the input one. This topology is depicted in Fig. 1.2b. This time the inductor is connected on the input and its second pole is switched between ground and  $V_{OUT}$  again using two switches.

The low-side switch is realized using NMOS transistor and for the high side switch again both NMOS and PMOS can be used. However, when the generated output voltage is high it may become impractical to use integrated on-chip transistor (the higher the required voltage capability, the larger the area the transistor occupies). In this case a shottky diode is used in place of  $M_{\rm HS}$ .

The active phase starts when  $M_{LS}$  is active. The voltage across the inductor is  $V_{IN}$  and the inductor current increases with slope  $V_{IN}/L$ . In the second phase,  $M_{HS}$  is active instead and the inductor current discharges into the output capacitor and the load, dropping at a rate  $(V_{OUT} - V_{IN})/L$ .

The output voltage is then given as (again assuming ideal case and CCM operation)

$$V_{\rm OUT} = \frac{1}{1 - D} V_{\rm IN}.$$

(1.4)

### 1.3 Anatomy of switching converters

The switching converters is a very broad topic and it is beyond the scope of this thesis to cover it entirely, thus only an example of what a typical buck converter is composed of is given. A block diagram of such a converter is in Fig. 1.3. The detailed study of each IP would take a book to cover, thus only a brief summary with the most important parameters is given.

#### **Power MOSFETs**

A feasibility study of every switching converter design starts with estimation of power transistors that make the switching half-bridge, i.e.  $M_{\rm HS}$  and  $M_{\rm LS}$ . These transistors usually consume the largest silicon are of all blocks and directly impact efficiency both at high load and low load conditions.

At high load currents the converter losses are dominated by conduction (ohmic) losses due to (but not only) on-state resistance of the power transistors. The respective power losses for the buck converter are

$$P_{\rm LS} = (1 - D)R_{\rm LS} \left( I_{\rm load}^2 + \frac{\Delta I_L^2}{12} \right), \tag{1.5}$$

$$P_{\rm HS} = DR_{\rm HS} \left( I_{\rm load}^2 + \frac{\Delta I_L^2}{12} \right), \qquad (1.6)$$

where  $I_{\text{load}}$  is the load current,  $\Delta I_L$  is the peak-to-peak ripple of the coil current and  $R_{\text{LS}}$ and  $R_{\text{HS}}$  are on-state resistance of the low-side and high-side power paths, respectively. The last two include not only the on-state resistance of the power transistors themselves but they include also the metalization up to the pin of the device. Significant layout effort is put to

#### 1. Introduction

Figure 1.3: Block diagram of buck converter.

minimize the effect of metals and it is common to use special software for mesh analysis [4].

At low load currents the efficiency is limited by switching losses that linearly scale with switching frequency. The power transistor switching losses are caused by body diode conduction or by charging gate, gate-drain and drain capacitances. These effects scale with transistor size, there is therefore trade-off in power MOS size selection between conduction and switching losses.

To alleviate the switching losses one can divide the power transistor and turn-on only a fraction at light loads (one such a circuit is presented in [5]). The most common solution is, however, to scale down the switching frequency. This mode of operation is usually called pulse-skipping or pulse frequency modulation (PFM) mode.

The body diode conduction happens when there is a gap between one transistor switching off and the other on. During this time the coil tries to maintains its current and pushes the LX node below ground (or above  $V_{\rm IN}$  in case of negative current, see ZCD) turning on the body diode of  $M_{\rm LS}$ . Depending on particular technology process, this may turn on lateral or vertical parasitic BJTs and cause e.g. increased consumption or substrate injection deteriorating analog circuit performance. For this reason the analog circuit on the same die should have high substrate rejection ratio. To alleviate these problems it is sometimes necessary to put a barrier around the power transistors<sup>4</sup> which further increases the area of the power section.

<sup>&</sup>lt;sup>4</sup>The problematic and type of such barriers is dependent on a particular technology at hand and is out of scope of this thesis.

Figure 1.4: Inductor current waveform along with (a) current sensor (on phase sensing), (b) ZCD and (c) OCD outputs (not to scale).

#### Drivers

As stated above, power MOS transistors tend to have a very large area and consequently large gate-source  $C_{gs}$  and gate-drain  $C_{gd}$  capacitances.

The power transistors thus require a strong driver capable of delivering enough current to the gates to turn the power transistors on and off in a very short amount of time (in the range of nanoseconds). Moreover, the driver must be able to keep the power MOS off during abrupt transitions on the switching node LX as these might accidentally pull the gate up (in case of NMOS) through the  $C_{\rm gd}$  capacitance. On the other hand, the transitions initiated by the driver should not be too fast as these cause large voltage spikes on bond wires and PCB metal parasitic inductances and can cause poor EMI performance or even some component voltage breakdown.

Another problem that must be prevented is a cross conduction during switching transition both in the power transistors and the drivers. This is usually solved by using feedback from the gate of the other transistors into the driver (see cross coupled feedback in the drivers in Fig. 1.3) and blocking turn-on until the other transistor turns off.

#### Current sensor

Measuring inductor, input or output current is used in DC-DC converters for several purposes. Multi-phase converters use the values of its inductor currents to balance the load across its phases. USB powered battery chargers measure input current value to regulate and guarantee they do not take more than the predefined current from the input.

The most power demanding and predominant type of current sensor used in switching converters senses inductor current in on or off phase as depicted in Fig. 1.4a. Various regulation loop architectures, such as current control mode (see below), use the value of inductor current in on phase or off phase to terminate that phase when the current reaches a particular value. On phase current sensor also sometimes precedes over-current protection circuit (see below). The power demand comes from the required speed of this type of sensor. Given that current consumer converters operate at switching frequencies above 1 MHz the on phase duration can be as low as 10 % of it, i.e. below 100 ns. Another important parameters include linearity, time required to stabilize upon turn on or input offset.

#### Zero crossing detector

When the converter is heavily loaded, the power stage alternates between low-side and highside transistors creating a triangular inductor current waveform with an average value equal to output load current. This mode is called continuous conduction mode (CCM) and can be seen in Fig. 1.4. However, if the load dropped to a small value the inductor current would still maintain a triangular waveform but part of the waveform will be below zero. In the extreme case of a zero load the inductor current would ripple around zero. Although the converter would operates with no load it would still dissipate a lot of power due to the conduction and switching losses.

To overcome this adverse effect it is common to turn  $M_{LS}$  off just before the inductor current reverses polarity thus limiting it to positive values only. When this happens the converter is said to operate in a discontinuous conduction mode (DCM).

Historically, a shottky diode was used in place of  $M_{LS}$  and no control was necessary. With the need for higher efficiency power transistors are preferred and a dedicated sensor is needed to emulate the diode behavior.

The sensor that allows that is called zero crossing detector (ZCD), zero comparator (ZCOMP) or sometimes discontinuous mode detector (DMD). This comparator usually senses voltage drop on  $M_{LS}$  (in buck  $M_{HS}$  in boost) and triggers on zero crossing as depicted in Fig. 1.4b. Although the ZCD is supposed to trigger at zero current setting some small threshold even for zero crossing detection allows to compensate for the delay of the system between the crossing of the threshold and the actual turning off of the power MOS. This early ZCD trigger incurs less power dissipation than letting the coil current reverse direction [6]. The comparator threshold should be therefore set as

$$V_{\rm ZCD} = -R_{\rm dson} \frac{V_{\rm OUT}}{L} t_{\rm dly}, \tag{1.7}$$

where  $R_{dson}$  is the on-state resistance of  $M_{LS}$ , and  $t_{dly}$  is the system's delay which comprises of ZCD, control logic and drivers delay. However, when the load is small the positive peak of the inductor current can be small and the time it takes to reach the zero can be smaller than  $t_{dly}$ . Hence, it is necessary to minimize  $t_{dly}$  and consequently the delay of the ZCD itself which leads to high current consumption of this block. Another important factors are input offset voltage or start-up time.

#### Over current detector

When the converter gets overloaded or the output is even shorted the current in the inductor can get higher than what is safe for correct operation of the circuit. To overcome this the converters feature a circuit called over current detector (OCD) or over-current protection (OCP).

Figure 1.5: Control types: (a) Voltage mode control (VMC), (b) current mode control (CMC).

The common way to design such a protection is to stop the on phase (the one in which the current is increasing,  $M_{HS}$  in this case) once the inductor current crosses a predefined maximum value. This behavior can be seen in Fig. 1.4c. Depending on the design of the converter, the inductor current can be let discharged all the way to zero before a new cycle is started or the whole converter can be shut down. The latter case is called hiccup mode, after some timeout the converter attempts to start again.

The most important parameter for such a comparator is propagation delay, but unlike ZCD input offset voltage is not of the most importance since threshold is given as  $V_{\text{OCD}} = R_{\text{dson}}I_{\text{OCD}}$  and is in the range of hundreds of millivolts.

#### **Regulation controller**

There are many ways to control the switching converters, analog or digital, synchronous or asynchronous, etc. Two of the most common are described next.

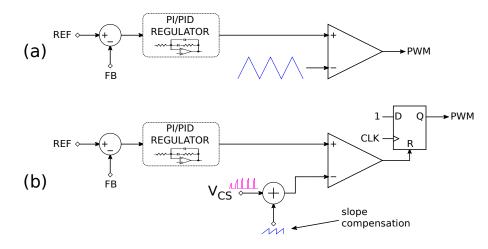

Voltage mode control (VMC) is depicted in Fig. 1.5a. The difference between the reference voltage and the feedback taken from the (divided) output goes into an analog PID regulator (usually called error amplifier) whose output is then compared to a sawtooth or triangular waveform from an oscillator to produce a digital PWM signal to drive the switching of power transistors. The comparison to the periodic waveform makes the system periodic and as such must be analyzed. The triangular waveform is preferred for comparison as it crosses-samples the amplified error signal twice in a period allowing for a higher loop bandwidth [7].

In peak current mode control (CMC), depicted in Fig. 1.5b, the active phase (PWM=1) starts with a clock from the oscillator. The output of the current sensor is then compared to the amplified error and when it crosses the active phase is terminated. The output of the PID regulator is thus proportional to the peak current in the inductor. However, pure CMC suffers from subharmonic instability for duty cycles > 50%. The common way to solve it is the so called slope compensation - superposing current sensor output with a ramp signal essentially combining CMC with a bit of VMC. Although CMC is more complex than VMC, it allows for simpler compensation and higher loop bandwidth.

In both cases the output of the PID regulator is clamped to fall within the bounds of the triangular waveform. If this protection was not implemented the amplified error would drift away when the converter is not in regulation (this can happen e.g. in bypass mode, when the output is overloaded or in no load conditions) and it would take time to slew back to the regulation region. This would produce overshoot or undershoot out the output.

#### **Control logic**

Control logic controls the behavior of the switching system. It gathers information from the regulation controller, ZCD, OCD and other parts of the systems and decides on the state of the system, whether to enter bypass mode, pulse-skipping or PFM mode and whether to switch low-side or high-side power transistors. Since it must react to immediate events it is implemented as asynchronous state machine, hand drawn from logic gates or synthesized from Simulink models.

#### Voltage reference and DAC

Every switching regulator contains a reference voltage generator - a bandgap reference. The output of the bandgap reference can be followed by a reference DAC which allows to set different output voltage settings. This method is preferred over changing feedback divider ratio as it changes also the loop gain and complicates compensation.

#### Softstart

If the converter started immediately with full voltage reference it would overshoot the desired output voltage and could damage the following circuitry. Also any short on the output would cause rapid inductor current build-up and potentially destruct the device. For this reason the reference voltage to the regulator and consequently the output voltage is slowly ramped up using a dedicated softstart block.

The softstart is usually implemented as charging a capacitor with a constant current or, if the reference DAC has high enough resolution, it can be done by ramping the digital value of the DAC.

#### Oscillator

Synchronous switching converter are usually synchronized by trimmed local oscillator. It must usually produce not only a digital waveform for control logic but also a sawtooth or triangular waveform depending on the type of the regulation controller.

In order to pass strict EMI rules frequency spreading can be implemented to reduce the peaks in the noise spectrum the converter generates. This can be implemented both in analog or in a digital way simply by changing the trimming bits of the oscillator by a pseudo random sequence.

#### Thermal protection

Since the integrated power transistors produce heat there is a risk of over-heating and potential destruction of the chip when it is not properly cooled. Every switching converter therefore features thermal protection circuit which suspends operation when the temperature on the die reaches a certain threshold. Due to the relatively low thermal conductivity and large thermal time constants the temperature difference on the die can be over 10°C thus the thermal sensor should be placed as close to the power transistors as possible. For large SoC chips it is not uncommon to have several thermal sensors.

#### Linear regulator

Even though some switching converters already serve to generate low output voltage they need a way to power their internal circuitry from a high input voltage. For this reason a linear regulator can be present on the chip. It must have a good PSRR and substrate rejection ratio to not propagate the switching noise to the internal circuitry. If the consumption of the chip is high it deteriorates low load efficiency. In some cases the power supply of the internal circuits can then be switched to the output of the converter to take advantage of the better efficiency of the switching converter.

### 1.4 Thesis motivation

With the advent of portable consumer devices, such as smartphones, notebooks or smartwatches there has been continuous push for smaller (and thinner) and more power efficient application. The size constraints apply not only to ICs but also to the surrounding passive components, such as capacitors or inductors. In the context of switching converters, smaller capacitors are less capable to handle load variation which increases requirements on the reaction time of the switching converters and consequently on their switching frequency. However, higher switching frequency and smaller inductors in turn require faster analog circuitry inside the chip and therefore higher power.

Another trend to increase efficiency and cut down cost is to use higher supply voltage to deliver power to the application. This allows to use lower current and consequently thinner wires. One example, where this practice can be seen, is the charging of portable battery operated devices through USB using higher input voltage, such as USB Power Delivery [8] (up to 20 V) or Qualcomm Quick Charge (up to 22 V) standards.

The use of high voltages puts again emphasis on area of the blocks as they need to use special structures, such as DMOS transistors, to handle the high voltages<sup>5</sup>, which take up a lot of silicon area.

The analog blocks which are affected the most by these demands are the ones which process the inductor current information as their requirements for speed scale with switching frequency. These blocks include current sensors, zero crossing and over current detectors. Moreover, the current information is usually sensed in high voltage domain (e.g. on highside power transistor) which further complicates the design. One other block whose requirements scale with switching frequency is the oscillator. With the rest of the mentioned blocks it shares the same property of dealing with fast triangular signals and thus similar design techniques can be used.

As will be seen in the dedicated chapters, current solutions of these circuits often rely on standard structures and when facing requirements written above they take large area

<sup>&</sup>lt;sup>5</sup>In the context of IC design, this usually means anything above the maximum allowable gate voltage, usually 5 V.

or power. This is especially true for non-standard applications which could benefit from dedicated new architectures.

## 1.5 Goals of the thesis

The goal of this thesis is to give an overview and outline design problems with the aforementioned blocks and contribute to development with regard to power, silicon area and high voltage capability requirements, especially for non-standard applications. These goals are:

Design high voltage bidirectional current sensor with off-chip inductor current sensing reducing area and need for special components. Standard solutions for off-chip sensing use operational amplifiers with both high voltage input and output. This complicates design because all the basic structures must be cascoded with high voltage components and consequently take a lot of silicon area. Moreover, bidirectional sensing is complicated and would load the sensing circuit.

**Explore new architectures of triangle waveform generation for use in SMPS**. With increasing demand for small form surface mount packages silicon area of every block can have an impact on whether the final design fits into the package or not. Standard solutions require two fast comparators or complex functional blocks consuming power and taking unnecessary silicon area.

**Evaluate the possibility to combine OCD and ZCD functions for use in special combined converters, such as battery charging chips**. Battery chargers combine buck and boost functionality in one circuit, both of which require overcurrent and zero crossing detectors. However, no combined OCD and ZCD solution has been presented so far. Having these functions in one IP would reduce area of the system, this is even more pronounced in multi-phase systems.

Find OCD solution mitigating reference kickback noise and slow startup. In ultra low power converters (quiescent current in the range of  $\mu$ A or less) the OCD circuit must be turned off when not immediately in use. The sudden switching on and off causes kickback noise on the bias lines that can propagate to the rest of the circuit. Moreover, biasing the block with low bias current causes long start-up times which complicates turning it on on a cycle-by-cycle basis. Sometimes, the block is enabled only when output voltage drops below regulation, but this may not protect the chip in sudden short on its output.

## 1.6 Organization

The organization of this thesis is as follows. Chapter two gives brief overview of current sensors and continues with a development of high voltage current sensor based around a differential difference current conveyor (DDCC) with high voltage input stage and gain trimming.

Chapter three deals with triangular waveform generating relaxation oscillators and presents a new topology suitable for DC-DC converters. This new relaxation oscillator employs only one low area comparator with accurate hysteresis set by a bias current and a resistor.

Chapter four is about current comparators. After an overview of ZCD and OCD architectures a new dual purpose high voltage buck over current/boost zero crossing detector is presented, followed by a new overcurrent detector with built-in reference.

Conclusion in chapter six gives a brief summary of the work done a gives an overview of the publication activity of the author.

## 2 Current Sensors

This chapter deals with current sensors, more specifically, current sensors for switching DC-DC converters sensing inductor current either continuously, or in a specific phase of the switching cycle (according to the needs of a particular control loop).

An overview of different current sensing principles can be found in [9, 10]. When the power MOS transistors are integrated on-chip the copy or sense MOS technique is used. For applications with off chip power transistors other techniques measuring inductor current must be used.

The next sections look into the most used sensing principles more in detail. Development of a novel high voltage current sensor follows.

### 2.1 On-chip inductor current sensing

Although many current sensing techniques exist [9] only few can be used for applications requiring sensing on on-chip power transistors. The sense-MOS technique of current sensing is well established and used throughout industry.

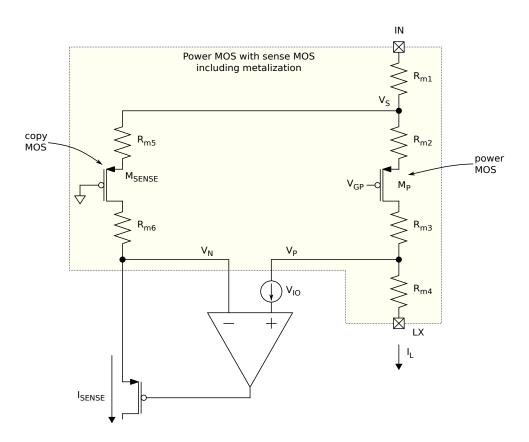

The principle of operation is depicted in Fig. 2.1. As described in the previous chapter the power MOS transistor in an SMPS operates as a switch. When turned-on its IV characteristic (for low  $V_{DS}$ ) can be approximated by the one of an equivalent resistor

$$R_{\rm dson} = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{GS} - V_{TH})},$$

(2.1)

where  $\mu$  is the mobility of the respected current carriers,  $C_{ox}$  is the gate oxide capacitance per unit area, W and L are the width and length of the transistor, respectively and  $V_{TH}$  is the threshold voltage. When the inductor current  $I_L$  flows through the power transistor  $M_P$  it develops drain-source voltage  $V_{DS} = R_{dson}I_L$ . This voltage is then forced with an operational amplifier onto second transistor  $M_{SENSE}^{-1}$  whose current is then sent for processing. Because both  $V_{GS}$  and  $V_{DS}$  of the transistors are the same the ratio of the sense and coil currents is equal to the ratio of their  $R_{dson}$  and therefore their widths (length is always the same for both transistors to equalize short channel effects)

$$I_{\text{sense}} = I_L \frac{R_{dsonP}}{R_{dsonS}} = I_L \frac{W_{\text{sense}}}{W_P},$$

(2.2)

where  $R_{dsonS}$ ,  $W_{sense}$  and  $R_{dsonP}$ ,  $W_P$  are the on-state resistances and total widths<sup>2</sup> of the sense and power transistors.

Given the constraints on power consumption the ratio of widths can be as low as  $10^{-4}$  or even  $10^{-5}$ . It can then happen that the width of the  $M_{\text{SENSE}}$  reaches the limits of the given technology. However, this is undesirable as the narrow channel effects will change  $M_{\text{SENSE}}$ parameters and consequently deteriorate ratio accuracy across temperature. Moreover, too small sense transistor will experience large mismatch and further ratio accuracy. Instead, it

<sup>&</sup>lt;sup>1</sup>An alternative term for sense MOS is copy MOS.

<sup>&</sup>lt;sup>2</sup>Counting all transistor modules and fingers.

Figure 2.1: Sense/copy MOS current sensing technique.

is possible to reduce the ratio by stacking several modules of sense transistor in series. An example of this practice can be found in Chapter 4.

In reality the on-state resistances are not the sole ones that contribute to the total path resistance. Metal interconnection as well as bond-wire or ball resistances can contribute significant portion of the total resistance, especially for high current applications requiring very low total resistance. The power transistor is spreads across large area and divided into fingers and so the metal contributions are distributed. For further analysis a surrogate model in Fig. 2.1 is used. Another detrimental effect is due to the input offset voltage  $v_{io}$  of the operational amplifier. Taking all this into account the sensed current can then be expressed as

$$I_{\text{sense}} = I_L \frac{R_{dsonP} + R_{m2} + R_{m3}}{R_{dsonS} + R_{m5} + R_{m6}} + \frac{v_{\text{io}}}{R_{dsonS} + R_{m5} + R_{m6}},$$

(2.3)

where  $R_{m2}$ - $R_{m3}$  and  $R_{m5}$ - $R_{m6}$  are metal and bond-wire resistances of the surrogate model.

Since metal and transistor resistances have different temperature coefficients it is necessary to balance the sense path metals denoted by  $R_{m5}$  and  $R_{m6}$  to be in the same proportion to  $R_{dsonS}$  as  $R_{m2}$  and  $R_{m3}$  is to  $R_{dsonP}$ , thus keeping the same ratio across temperatures. The temperature stability is also closely related to the position of  $M_{SENSE}$  in layout. As the power transistor heats up during operation  $M_{SENSE}$  should be placed close to it so they are at the same temperature.

As can be seen position of  $M_{\text{SENSE}}$  and its connection  $M_P$ , as well as picking up sensing nodes  $V_N$  and  $V_P$  is not an easy task. It must be done carefully with the help of post-layout metal extraction or even using specialized software [4].

Figure 2.2: High-side current sensor transient response example (sensor output scaled to facilitate comparison).

The effect of operational amplifier's input offset voltage from Eq. 2.3 can be converted back to the inductor current as input current offset

$$I_{Loff} = \frac{v_{io}}{R_{dsonP} + R_{m2} + R_{m3}}.$$

(2.4)

Given power path resistance of  $100 \text{ m}\Omega$  an offset voltage of 1 mV will induce inductor measurement error of 10 mA. For over-current protection offset is usually not a problem since the threshold is usually in the range of amperes. For regulation purposes the mere offset may not be a problem as the integrator (see previous chapter for system description) will compensate it. However, negative offset will create a dead band at low current readings.

As the sensing is done only on one transistor the inductor current is sensed only in part of the switching period. In the rest of the period the switched inductor node LX is tied to the opposite power supply by second power transistors. During this time the input of the operational amplifier must be protected from this high voltage. The system thus contains a masking circuit which enables the current sensor (or just connects its input to LX node) only when it is safe, usually on the basis of voltage on LX and gate voltage of the power MOS.

A transient output example of a current sensor is depicted in Fig. 2.2. As stated above, sensing is enabled or unmasked only when the particular power MOS is on. When this happens the output of the current sensor needs some time  $t_{\text{settle}}$  to settle and to start follow the input current. This time is influence by many factors, such as bandwidth and phase margin of the current sensors or whether the LX node itself already settled to a value given

Figure 2.3: Sense MOS current sensor: (a) amp. w/ common source stage, (b) common gate amplifier.

by the resistance of the power path. Due to these effects and also due to possible capacitive coupling the output of the sensor can overshoot. This is a problem over-current protection or some regulator architectures (such as peak-current mode) as these could prematurely trigger. It is therefore common to generate another masking signal that indicates the output of the current sensor is valid and mask further circuits from processing current sensor output during its settling time.

Due to a finite bandwidth  $f_{BW}$  the current sensor tracks the input waveform with a delay. This delay can be estimated for a one pole system as

$$t_d = \frac{1}{2\pi f_{\rm BW}}.\tag{2.5}$$

#### **Amplifier topologies**

Now we will focus on the transistor topologies used for the amplifier. Fig. 2.1 uses operational amplifier with a source follower. In order to guarantee correct operation a folded cascode amplifier must be used to be able to process high input common mode voltages close to the supply line. One such a solution was presented in [11].

Instead of using source follower, the operational amplifier can drive a common source stage [12] as depicted in Fig. 2.3a. The common source transistor  $M_1$  together with  $M_2$  form a current mirror so the output current can be taken from  $M_2$ . Adding another output transistors to this current mirror we can easily distribute current information to different parts of the system.

Figure 2.4: Off-chip inductor current sensing:(a) on external resistor and (b) filter-based sensing on coil resistance.

Instead of using traditional gate input operational amplifiers, more common practice is to employ simpler stages with common base [13] or common gate [14–17] amplifiers as can be seen in Fig. 2.3b. The differential input voltage  $V_P - V_N$  is sensed through sources of  $M_1$  and  $M_2$  which form a source driven differential pair. Since it is loaded with a current source  $M_5$  the gain of the stage can be written as  $g_{m2}(r_{o2}||r_{o5})$ , where  $g_{m2}$ ,  $r_{o2}$  and  $r_{o5}$  are the transconductance and output resistances of the respective transistors. Although not shown, for higher output resistance and consequently higher gain the transistors  $M_1$ - $M_2$ and  $M_4$ - $M_5$  are usually cascoded. Cascodes are also important when high voltage capability is requested since they can provide the necessary protection from over-voltage on the main matched transistors<sup>3</sup>.

Transistors  $M_{S1}$  switches the  $V_P$  node to LX when  $M_P$  is turned-on and sensing takes place. Otherwise  $V_P$  is switched to IN using  $M_{S2}$  thus making zero differential voltage and therefore zero output current (neglecting offset). This way the voltages of the sources of the differential pair are always close to each other so that they are stressed the same and protected from high voltage of LX. If this was not the case the unequal stress would cause offset shift over time or even damage of  $M_2$  if  $V_{\rm IN} - V_{\rm LX}$  went beyond its save operating area.

One drawback of the common gate amplifiers is their input currents  $I_1$  and  $I_2$ , as  $I_1$  creates a drop on  $M_{\text{SENSE}}$  and therefore induces input offset voltage of  $R_{dsonS}I_1$ . As in regulation  $I_1 \doteq I_2$  one can introduce the same offset drop also in the second amplifier input if, for example,  $M_{S1}$  is sized the same as  $M_{\text{SENSE}}^4$ .

### 2.2 Off-chip inductor current sensing

For applications with off chip power transistors other techniques measuring coil current must be used.

One way of measuring coil current uses a sensing resistor in series with the coil as depicted in Fig. 2.4a. This has the disadvantage of introducing additional loss into the system and lowering overall efficiency. Other method uses the parasitic resistance of the coil (DCR) to measure the current [9]. This is done by adding a filter in parallel to the coil as shown in

<sup>&</sup>lt;sup>3</sup>High voltage transistors, such as DMOS, tend to have worse matching properties so they are not used in places where precise matching is required.

$<sup>{}^{4}</sup>R_{dson}$  of  $M_{P}$  doesn't induce any error as it is negligible due to the very high ratio of  $M_{P}$  and  $M_{SENSE}$

Figure 2.5: Off-chip sensing architectures:(a) transconductance amplifier, (b) drop compensation amplifier.

Fig. 2.4b, where  $R_L$  represents a DC resistance of the coil. If the following condition holds

$$RC = \frac{L}{R_L},\tag{2.6}$$

then the voltage on the capacitor is proportional to the inductor current as

$$v_C(t) = R_L i_L(t).$$

(2.7)

One of the circuits sensing off-chip inductor current is presented in [18]. The sensing principle is depicted in Fig. 2.5a. It uses transconductance amplifier to sense the capacitor voltage proportional to the inductor current. However, as the transconductance in [18] is realized by a differential pair the process and temperature variations make current readings inaccurate.

The sensing circuit presented in [19], depicted in Fig. 2.5b, uses an operational amplifier and a source follower to sink current from a resistor  $R_{\text{DROP}}$  and equalize its drop to the one on sense resistor  $R_{\text{SENSE}}$ . This is in fact similar principle as the one in Fig. 2.1 and the same circuit topologies can be used here. The same principle is also used in [20], where the current sensors uses the current shunt monitor chip INA139. However, these circuits do not support bidirectional current sensing.

The circuit in [21] uses instrumentation amplifier to sense the coil current, however, it requires high voltage operational amplifiers. Another solution [22] uses capacitors to sample the input voltage but it requires capacitors with high voltage capability. These are usually available only as metal-metal capacitors and as such consume a lot of silicon area.

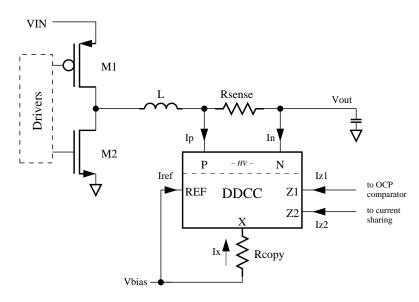

Another solution was proposed by the author of this thesis in [C]. The block diagram of this current sensor is in Fig. 2.6. The basic building block is the DDCC [23] with multiple outputs which is described in ideal form as

$$I_{\text{REF}} = 0, \ I_P = 0, \ I_N = 0,$$

(2.8a)

$$V_X = V_{\text{REF}} + \alpha (V_P - V_N), \qquad (2.8b)$$

$$I_{Z1} = I_{Z2} = I_X - I_{\text{off}}, \tag{2.8c}$$

Figure 2.6: Block diagram of a DDCC based current sensor.

where  $I_{\text{off}}$  is internally added offset current to allow simple bidirectional signal processing by the subsequent circuitry and the gain  $\alpha$  equals 1 for a traditional DDCC.

The sensed voltage difference on the  $R_{\text{sense}}$  is copied by the DDCC onto a resistor  $R_{\text{copy}}$ , therefore the output currents are proportional to the coil current as

$$I_{Z1,2} = \alpha I_L \frac{R_{\text{sense}}}{R_{\text{copy}}} - I_{\text{off.}}$$

(2.9)

The output currents are identical and can be easily added and scaled according to the various needs of the application. The  $V_{\text{bias}}$  is a constant inaccurate voltage selected in the common mode range of the inputs.

The analysis of the DDCC behaviour has been carried in [23]. For accurate  $\alpha$  the internal feedback loop must have a sufficient gain, this is guaranteed by cascoding of the internal current mirrors. Another major source of inaccuracy are the nonlinearities.

The main component of DDCC is a differential difference amplifier, its nonlinearities are analyzed in the next section.

#### 2.3 Analysis of a DDA

Differential difference amplifier (DDA) is one of the most used modern functional block first proposed in [24]. It is also a basic block for building other functional blocks such as DDCC [23]. The DDA has two inverting and two non-inverting inputs as can be seen from the symbol shown in Fig. 2.7a. The ideal DDA is governed by the following equation

$$v_{out} = A \left( v_{p1} - v_{n1} + v_{p2} - v_{n2} \right), \qquad (2.10)$$

where A is an open-loop gain of the DDA.

The DDA function is usually implemented by summing outputs of two transconductors and amplifying it. One of the possible CMOS implementations is in Fig. 2.7b. The output current of two differential pairs is summed and amplified by two stages.

Figure 2.7: Differential difference amplifier: (a) symbol, (b) example of CMOS implementation.

However, this process involves various sources of errors. First, the transconductors may not be fully linear in the whole input voltage range. This is especially true when the mere differential pairs are used as in Fig. 2.7b. Second, the gain of the two transconductors may differ, and third, the transistor mismatch and the potential asymmetry of the circuit causes offset.

The analysis of the open loop parameters of the DDA was carried out in [25], however, the parameters were derived only for MOS transistors in strong inversion using a square law model and it doesn't offer closed form solutions for DDA under feedback. This chapter focuses on the analysis of the DDA in unity gain configuration, which is used the most in various function blocks such as the aforementioned DDCC. Although the derivations are approximate the results are provide qualitative view on the studied system.

#### Differential pair nonlinearity

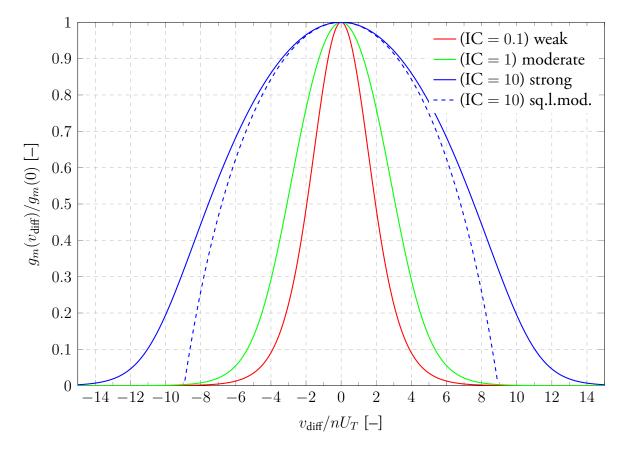

The nonlinearity of a differential pair can be seen in Fig. 2.8 which depicts a normalized transconductance of a differential pair with respect to its maximal value at zero input voltage. As the magnitude of the input differential voltage increases the transconductance drops. As will be seen next, this drop leads to nonlinearity of the DDA.

For evaluation of Fig. 2.8 a BSIM6/EKV model was used [26, 27] as it smoothly models all regions of operation (weak, moderate and strong inversion regions) of a MOS transistor and simplified equations for analysis are available. Using this model, the IV relationship for a transistor in saturation can be expressed as

$$I_D = \frac{W}{L} I_0 \text{IC.}$$

(2.11)

where W is a width of the transistor, L is its length,  $I_0$  denotes a technology current and IC stands for an inversion coefficient. Technology current is a parameter of the EKV model given as

$$I_0 = 2n\mu C_{\rm ox} U_T^2, \tag{2.12}$$

Inversion coefficient IC is a positive quantity and characterizes the level of inversion of a MOS transistor. It is dependent on the terminal voltages of the MOS transistors according

**Figure 2.8:** Dependence of the transconductance of a differential pair on input voltage difference for various bias conditions.

to the following equation (note that all voltages are referenced to bulk, e.g.  $V_S \equiv V_{SB}$ )

$$IC = \ln^{2} \left( 1 + e^{\frac{V_{D} - V_{S}}{2U_{T}}} \right) \cong \ln^{2} \left( 1 + e^{\frac{V_{G} - V_{T} - nV_{S}}{2nU_{T}}} \right),$$

(2.13)

where *n* denotes substrate factor,  $V_T$  threshold voltage,  $U_T$  thermal voltage<sup>5</sup> and  $V_P$  the so called pinch-off voltage, which can be linearly approximated around threshold voltage as  $V_P \cong \frac{V_G - V_T}{n}$ .

Using this model in Fig. 2.8, it can be seen that as the magnitude of  $v_{\text{diff}}$  increases the transconductance falls approaching zero and differential pair therefore stops transferring the signal. The closer the differential pair operates to weak inversion the steeper the drop of the transconductance is.

The x-axis is scaled to  $nU_T$  which makes this graph technology independent and will serve as the basis of further analysis.

The figure also presents transconductance analysis using a traditional square law model [28] (dashed line), however, it fails to correctly approximate the transconductance at higher input voltages as the transistor carrying less current falls into weak inversion.

<sup>&</sup>lt;sup>5</sup>Thermal voltage  $U_T = kT/q$ , the value for 300 K is 25.85 mV.

#### Analysis

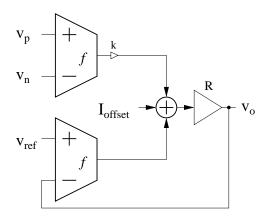

The simplified block diagram of the DDA in unity gain configuration can be seen in Fig. 2.9, where f denotes the transfer function of the transconductor and R is a cumulative gain

Figure 2.9: Simplified block diagram of DDA in unity gain configuration with major non-idealities.

of all the subsequent stages. The mismatch of tail currents of differential pairs can cause transconductances mismatch. This can be, in the first order, represented by a factor k. The offset is represented by  $I_{\text{offset}}$ . The function f itself is without offset and satisfies the following two conditions

•

$$f(0) = 0$$

,

• f(-v) = -f(v), i.e. function is odd.

Following Fig. 2.9, we can write

$$kf(v_p - v_n) + f(v_{\text{ref}} - v_o) + I_{\text{offset}} = \frac{v_o}{R}.$$

(2.14)

If k was equal to zero the circuit would be a simple operational amplifier and  $v_o$  would follow (with a gain error)  $v_{ref}$ . Adding the second current contributor  $kf(v_p - v_n)$  to the loop can be viewed as adding an offset, we can therefore without lack of generality change variables and analyze  $v_{out} = v_o - v_{ref}$  as a function of  $v_{in} = v_p - v_n$ . We then get

$$kf(v_{\rm in}) - f(v_{\rm out}) + I_{\rm err} = \frac{v_{\rm out}}{R},$$

(2.15)

where we used the fact that f is an odd function to push the minus sign out of the argument of f and for simplicity we grouped  $I_{\text{offset}} - \frac{v_{\text{ref}}}{R}$  into  $I_{\text{err}}$ . Because of the unity gain configuration the  $v_{\text{out}}$  is expected to be  $v_{\text{in}}$  except for some error  $\Delta$

$$v_{\rm out} = v_{\rm in} + \Delta. \tag{2.16}$$

Now if  $\Delta$  is small we can expand f at  $v_{in}$  using only the first term of the Maclaurin series

$$f(v_{\rm in} + \Delta) \doteq f(v_{\rm in}) + \Delta \left. \frac{\mathrm{d}f}{\mathrm{d}v} \right|_{v=v_{\rm in}} \equiv f(v_{\rm in}) + \Delta g_m(v_{\rm in}), \tag{2.17}$$

23

where we denoted derivate of f as  $g_m$ . Now using (2.16) and (2.17) in (2.15) we get

$$(k-1)f(v_{\rm in}) + g_m(v_{\rm in})\Delta + I_{\rm err} = \frac{v_{\rm in} + \Delta}{R}.$$

(2.18)

Solving for  $\Delta$  and adding  $v_{in}$  gives back expression for  $v_{out}$

$$v_{\rm out} = v_{\rm in} + \Delta = \frac{\left((k-1)f(v_{\rm in}) + I_{\rm err} + g_m(v_{\rm in})v_{\rm in}\right)R}{1 + g_m(v_{\rm in})R}.$$

(2.19)

Now all the terms use small signal quantities except for  $f(v_{in})$ . For very small  $v_{in}$  it can be approximated as  $g_m(0)v_{in}$ , however, a better approximation can be made using  $g_m(v_{in})$ (which is already present int the expression) if we look at Taylor's expansion of both f(v)and  $g_m(v)$

$$f(v) = \sum_{i=0}^{\infty} k_{2i+1} v^{2i+1} = k_1 v + k_3 v^3 + k_5 v^5 \dots$$

(2.20)

$$g_m(v) \equiv \frac{\mathrm{d}}{\mathrm{d}v} f(v) = \sum_{i=0}^{\infty} (2i+1)k_{2i+1}v^{2i} = k_1 + 3k_3v^2 + 5k_5v^4 \dots$$

(2.21)

Because f is odd function the expansion has only odd terms. Now if we approximate f(v) as

$$f(v) \approx \left(\frac{1}{3}g_m(v) + \frac{2}{3}g_m(0)\right)v = k_1v + k_3v^3 + \frac{5}{3}k_5v^4 + \dots$$

(2.22)

we see that it is able to reconstruct the first two non-zero terms of the expansion 2.20.

#### Gain and offset

The important circuit characteristics can now be expressed. Offset voltage is simply  $v_{out}$  evaluated at zero

$$v_{\text{off}} = v_{\text{out}}|_{v_{\text{in}}=0} = \frac{I_{\text{err}}R}{1+g_m(0)R} = \frac{I_{\text{offset}}R - v_{\text{ref}}}{1+g_m(0)R}.$$

(2.23)

Another important parameter is gain at zero input voltage

$$A_0 = \left. \frac{\mathrm{d}v_{\text{out}}}{\mathrm{d}v_{\text{in}}} \right|_{v_{\text{in}}=0} = \frac{kg_m(0)R}{1+g_m(0)R}.$$

(2.24)

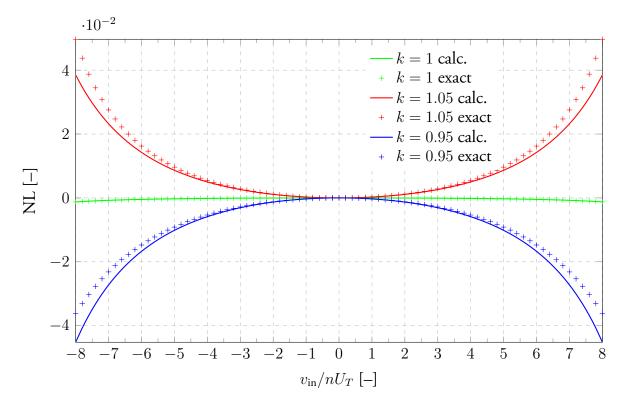

#### Nonlinearity

If transcoductance f was linear across the input voltage range, the output voltage would be also linear and given by  $A_0v_{in} + v_{off}$ . However the non-linearity of f leads to the nonlinearity of  $v_{out}(v_{in})$  relationship. This can be characterized using the nonlinearity parameter NL defined as a relative error with respect to the ideal linear behavior after the correction of gain and offset error

$$NL = \frac{v_{out} - v_{off}}{A_0 v_{in}} - 1.$$

(2.25)

Substituting (2.19), (2.23) and (2.24) into (2.25) we get the expression for nonlinearity

$$NL = \frac{1}{g_m(0)R} \left( 1 - \frac{1 + g_m(0)R}{1 + g_m(v_{in})R} \right) - \frac{I_{\text{err}}}{v_{in}g_m(0)k} \left( 1 - \frac{1 + g_m(0)R}{1 + g_m(v_{in})R} \right) + \frac{k - 1}{k} \frac{1 + g_m(0)R}{1 + g_m(v_{in})R} \frac{\frac{f(v_{in})}{v_{in}} - g_m(v_{in})}{g_m(0)}.$$

(2.26)

If we now use (2.22) we get

$$NL = \left(1 - \frac{1 + g_m(0)R}{1 + g_m(v_{\rm in})R}\right) \left(\frac{1}{g_m(0)R} + \frac{2}{3}\frac{1 - k}{k}\left(1 + \frac{1}{g_m(0)R}\right) - \frac{I_{\rm err}}{kg_m(0)v_{\rm in}}\right).$$

(2.27)

We can further simplify this expression by assuming  $g_m(v_{in})R \gg 1$ . This also implies that  $g_m(0)R \gg 1$  because  $g_m(0) \ge g_m(v_{in})$ . The final expression for nonlinearity is therefore

$$NL = \left(1 - \frac{g_m(0)}{g_m(v_{in})}\right) \left(\frac{1}{g_m(0)R} + \frac{2}{3}\frac{1-k}{k} - \frac{I_{\text{offset}} - \frac{v_{\text{ref}}}{R}}{kg_m(0)v_{in}}\right).$$

(2.28)